CPLDP-8

ハードウェア 製作編

omiokone

RAM

3.3V用12bit以上の巾のstatic RAMを探した結果 CYPRESS CY7C1041DV33 (256K×16 秋月電子扱い)にした。この石は0.8mmピッチなのでサンハヤトSSP-83変換基板を使用。

当初はメモリ空間4Kワードの最小構成のためほとんど余っていたが、現在はメインメモリ32Kワード、残り224KワードをRAMディスクに使用。

RAMディスクのバックアップは非選択時の電流が20℃の実測で1mAと大きいので割愛した。32Kワードはアドレスも配線してあったが、RAMディスクまで想定していなかった。もっとも、たまに遊ぶ分には電池の保守がめんどうなだけかも知れない。

2019年11月追記

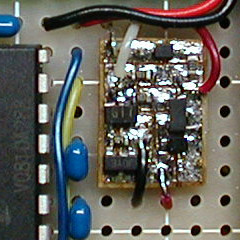

同じピン配置でスタンバイ電流1μAのCYPRESS CY62147EV30(Digi-Key扱い)を入手した。バックアップ電池回路は専用ICが高価なので、下図の回路を設計。チップ部品でモジュール化したが、使用トランジスタ、ダイオードは普通の小信号用のもの。

十数年前の設計時NEC μPD444012Aが候補だったが、注文の都合でCYPRESSのにしてしまった。RAMの換装をせずに済んだのだが。

水晶発振器

UFM読み出し回路の制限で主クロックは8.3MHz以下となるので8MHzを使用。この周波数はシリアル通信のボーレイトも決めるので注意。これだけ低クロックでもPDP-8の3倍程度の速さで動くのは1.5μsかかるコアメモリのアクセスがないため。

RS-232Cコンバータ

Intersil ICL3232CPZを使ったが3.3V用の同様のもので構わない。ただしチャージポンプのコンデンサは使用ICに合わせること。

その他

消費電流は5V入力の実測で50mAとLEDに10mA×16=160mA程度。USBから取ることも可能。ACなどのLED表示はハードのテストぐらいしか役に立たないので、消費電流と配線の手間から省略してもよいが、RUNとシリアル通信のビジーランプはあった方がよい。

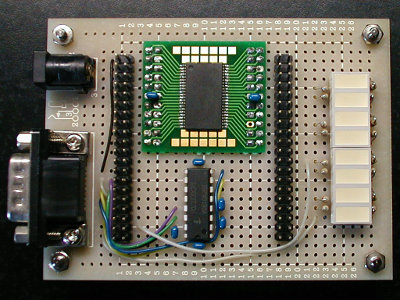

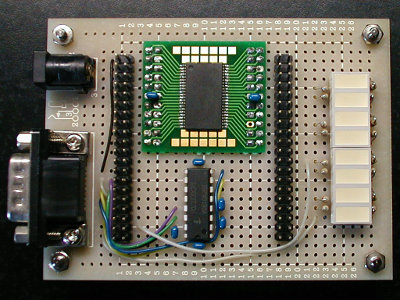

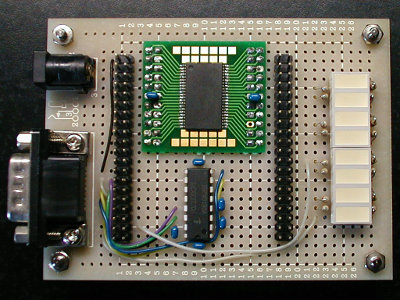

メイン基板としてサンハヤトのICB-93-CKを使った。これにはD-sub 9pinコネクタ(付属せず)とDC電源ジャック(付属)の取付穴があり便利。シリアルポートのコネクタはPCのものと同様のD-sub 9pin オスを使用。

初代PDP-8は上部が透明で内部基板が見えたのをまねて、透明アクリルケース(110×80×32mm)に組み込んだ。ケーブルに引きずられないようゴム足をつけておく。

試験中のCPLDP-8。MAXII書き込み用の25pinコネクタは完成後除去した。