Intel 4004の回路図を読む

6. マスクパターンを読む

omiokone

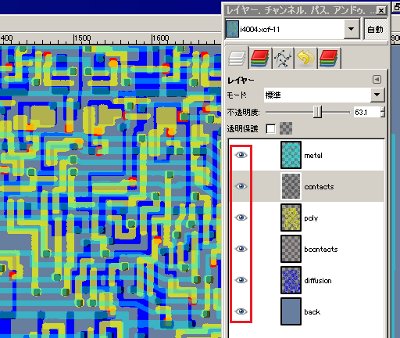

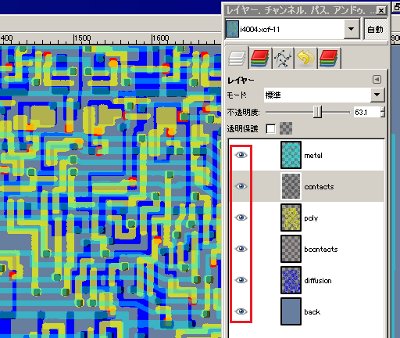

Intelのサイトにマスクパターンがあるが、あまり画質が良くない。35th Anniversary Projectでより鮮明なのが入手できる。同サイトには各マスクを合成して1枚のJPEGにしたものもあるが、込み入った部分が見づらい。そこで筆者がグラフィックソフトGIMP用の画像ファイルを用意した。

4004mask.zip

閲覧にはGIMPが必要だが各マスクがレイヤーになっており、下図の赤枠の部分の操作でマスクを表示/非表示にできる。パターンの表示窓の左下で表示倍率が変更できる。またGIMPに詳しい人なら、特定の線(例えばGND)を着色して解析するなどの操作も可能。

| GIMPレイヤー | 説明

|

|---|

| 色 | 名称

|

|---|

| 水 | metal | メタル(アルミ蒸着配線)

|

| 黒 | contacts | ポリシリコンまたは拡散層とメタルの接続

|

| 黄 | poly | ポリシリコン

|

| 赤 | bcontacts | ポリシリコンと拡散層の埋め込み接続

|

| 青 | diffusion | 拡散層

|

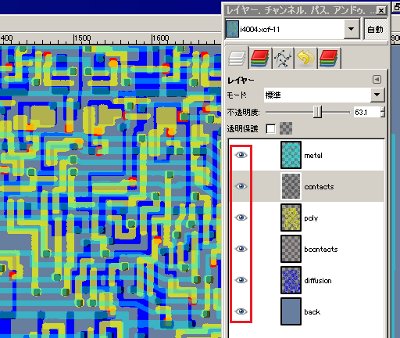

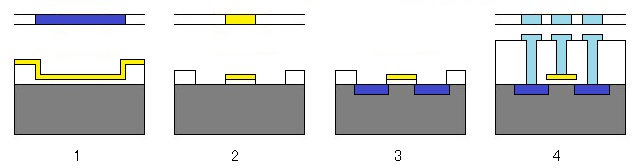

大ざっぱに各マスクの使われ方を解説する。以下でマスクを使ってとの記述は詳しくは、フォトレジストを塗布後マスクを使い露光現像、レジストのない部分をエッチングする作業である。当時は感光部分が残るレジストなので、ポリシリコンとメタルのマスクは着色部分が透明、それ以外は逆である。

n形ウェハ上に酸化膜を作った状態から始める。

- 拡散層マスクで最終的にFETとなる部分の酸化膜を除去し、改めて薄い酸化膜を形成。全体にポリシリコンを堆積する。図にはないが堆積前に埋め込み接続用マスクで酸化膜に孔を開け、拡散層とポリシリコンの接続部分にする。

- ポリシリコン用マスクでポリシリコン層をゲート電極または配線に加工する。酸化膜をエッチングする。この時ポリシリコンがレジストとなるためポリシリコンのない部分が露出する。

- ホウ素を拡散し、酸化膜のない部分がp形のソースドレイン領域となる。同時にポリシリコンも低抵抗化する。

- 上に厚い酸化膜を作り接続用マスクで孔を開けた後、アルミを蒸着してメタル用マスクで配線に加工する。

ポリシリコンは酸化膜の薄い部分、すなわち黄と青のマスクの重なった部分だけがゲートとして機能し、それ以外はただの配線となる。アルミの配線は厚い酸化膜で隔てられているので、メタルの真下にトランジスタなどがあっても干渉しない。メタルは一層なので配線の交差は拡散層やポリシリコンでくぐらせる。

当時はいくつかの技術、特にイオン注入が実用化前なので、製造プロセスは今の教科書に書かれているものと異なる原始的なものである。

代表的な部分について実際のパターンを見ていく。入出力端子以外の回路は前章までの解説も参照。

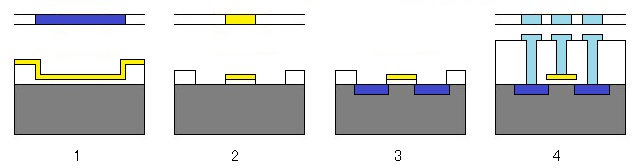

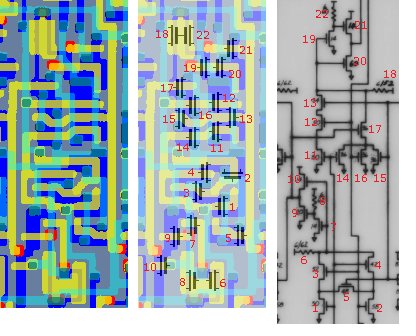

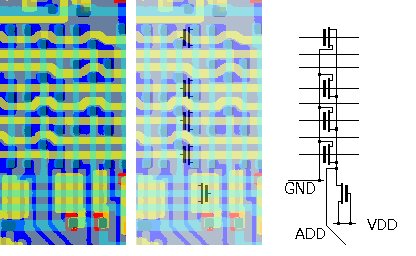

命令デコーダ

(左)ADD命令をデコードする部分。(中)前節の説明のように、ポリシリコンと拡散層マスクの重なった所がチャネルなので、これを手がかりにFETを書き込む。(右)FETどうしを結線。Intelの回路図を見ると4004は多くの部分で回路図と実際の素子配置がよく一致している。

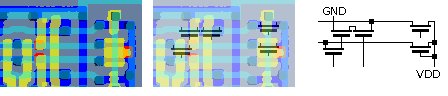

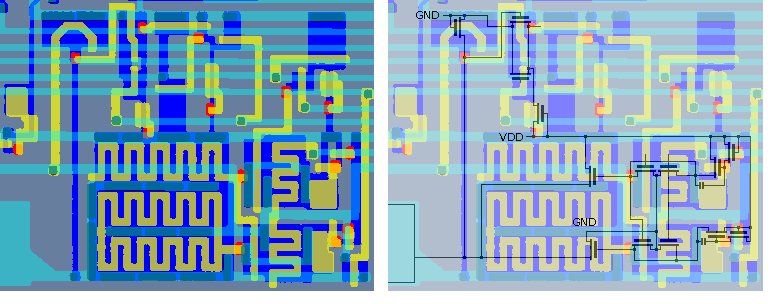

タイミング発生器

(左)リングカウンタのシフトレジスタ1段目。(中)Aの部分はポリシリコンに負電圧がかかると真下のn形シリコンに反転層ができ容量になる。右の2つのFETとともに1章で説明した負荷を成す。(右)Bが1段目の入力で各段のNORをとる信号線。

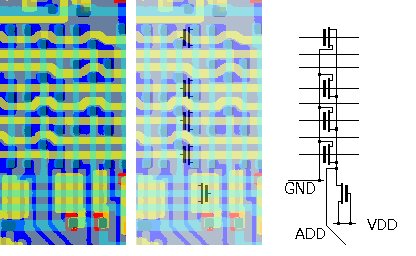

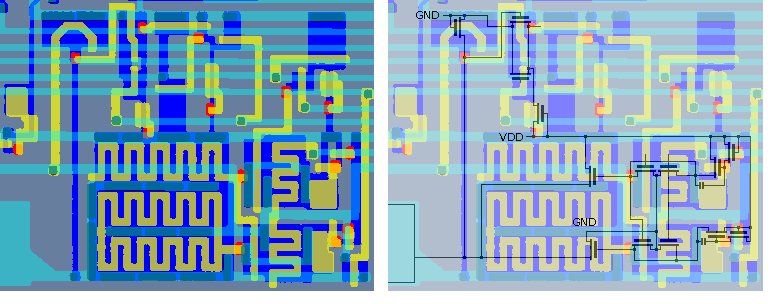

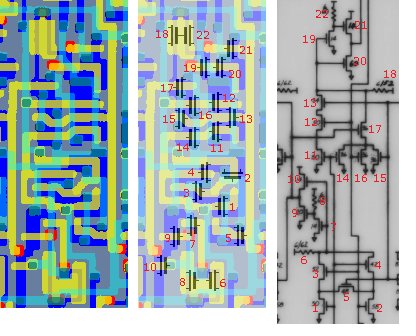

加算器

加算器のLSB部分で図を90°倒して示す。配線が入り組んでいるので、右の回路図に対応するFETを番号表示。11~13のFETは論理は同じだが回路図と接続順が異なり、実物はGND側から12 13 11の順。他の部分と比べて回路図と実際の配置の違いが大きく、キャリ伝播を短くする苦心がうかがえる。

インデクスレジスタ

左のFET 3個がインデクスレジスタ右上端の1bitセル。右の2個は上が読み出し線のプリチャージ用スイッチ、下が書き込み線の負荷。回路は単純だがセル1bitを切り分けるのに端から見ていく必要がある。セルのパターンは同時期のDRAM 1103のものとよく似ている。

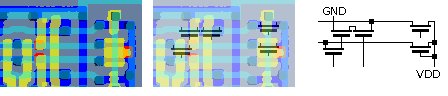

入出力端子

左下がD0入出力端子。出力FETとそれを駆動するFETは他の部分に比べ大きなもので、チャネル巾をかせぐためゲート/チャネル部分がジグザグになっている。左上のFETはゲートがGNDに接続され常にOFFだが、入力に高電圧が加わるとチャネルとソース/ドレイン間のPN接合が降伏して入力回路を保護する。

<5 | Intel 4004